TM 11-6625-3041-30 /TO 33A1-8-908-12

1-13. TRANSMIT 1 (A3) NRZ OUT (CONT)

The input from the Fam Sel is applied to the Pulse Gen, which

Pulse Gen

converts the symmetrical input to 120-ns wide pulses.

The output from the Pulse Gen is applied to an amplifier and

UNBALANCED

TMG OUT

through a filter to the front panel UNBALANCED TMG OUT connector.

PR Gen

The output of the Fam Sel is also applied to the clock input

of the PR (pseudorandom) Gen, which consists of a shift register

with feedback.

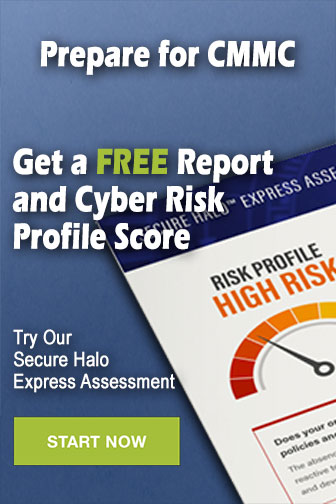

Upon application of

a clock pulse, an

input value is

accepted into the

first shift register

stage. With each

succeeding clock

pulse, the input val-

ue is shifted to the

next stage. With no

new input value, the

clock pulses will

eventually clear the

register.

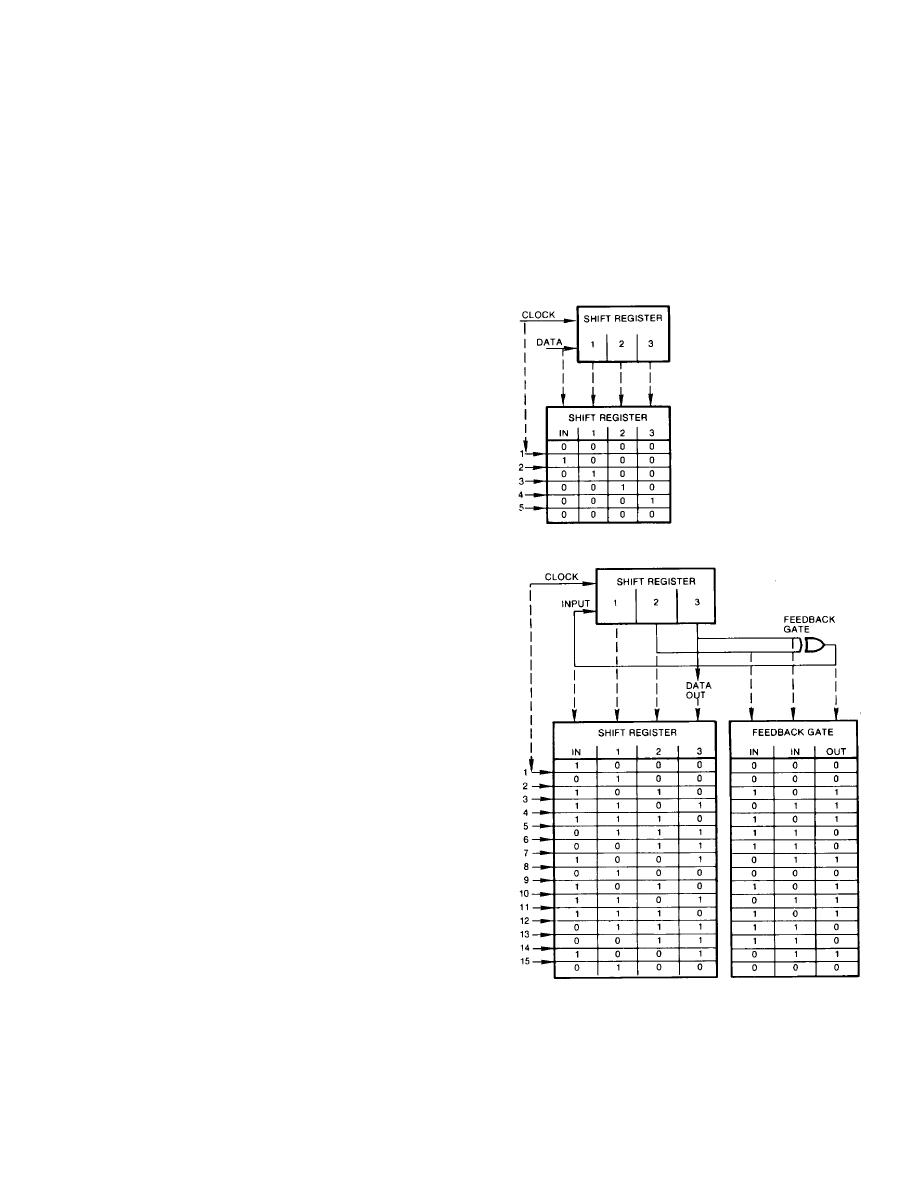

In a pseudorandom

generator, a feedback

path containing a

2-input exclusive-OR

gate is added to the

shift register. The

inputs to the gate

are taken from two

stages of the shift

register, and the

output is fed back to

the input of the reg-

ister.

The resultant data

signal out is a

repeating binary

sequence of ones and

zeros.

In the SG-1139 there

are 15 stages in the

shift reqister, which

produce a pattern of 32,767 bits. This pattern is long enough

so that the system under test responds as if the sequence was

truly random.

1-9