TM

11-6625-3041-30/T0

33A1-8-908-12

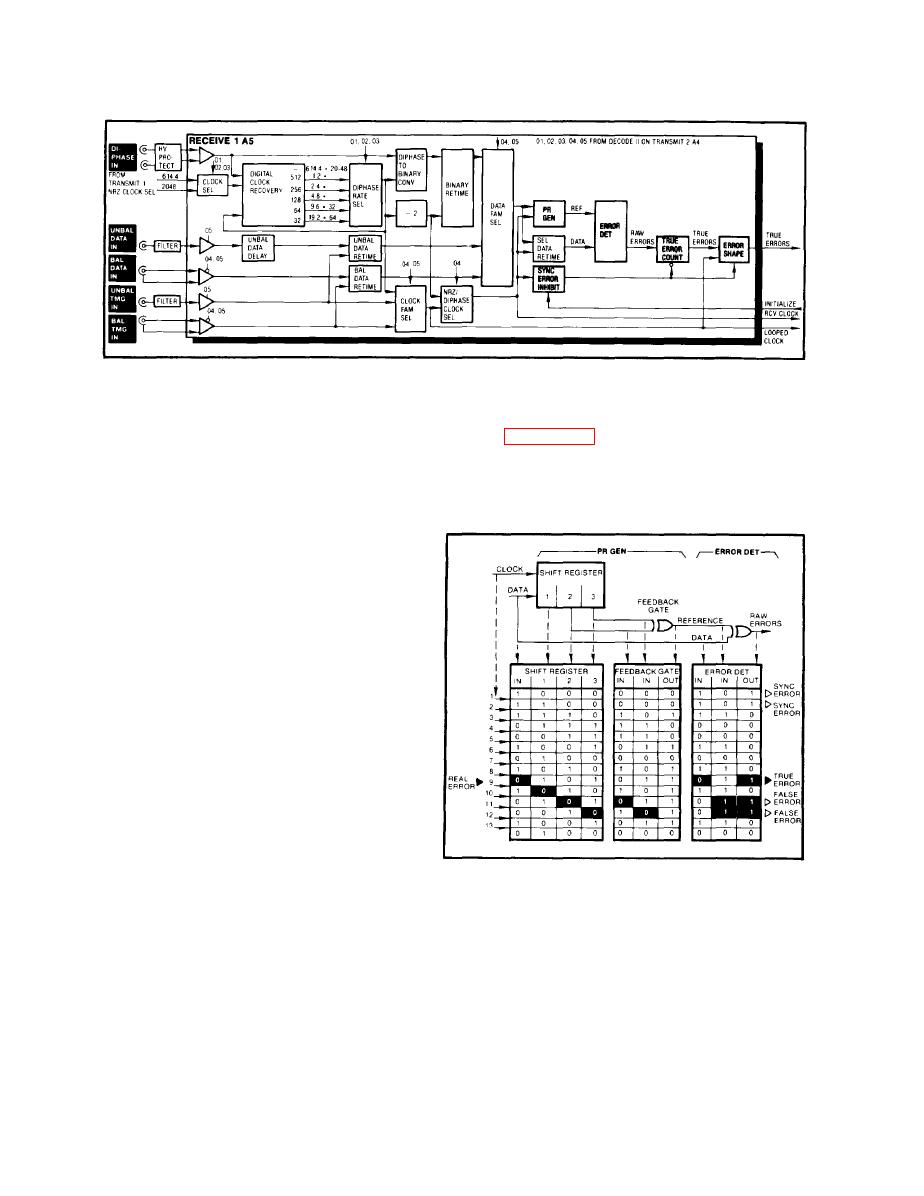

1-17. RECEIVE 1 (A5) ERROR DETECTION

PR Gen

The data output from the Data Fam Sel and the clock output

from the NRZ/Diphase Clock Sel are applied to the PR Gen.

This PR Gen is identical to the one used on the Transmit 1

card for data output (refer to para 1-13, PR Gen).

The clock input shifts the data input through the shift

register in the PR Gen. The outputs of the register are

applied to a feedback gate, which is an exclusive-OR gate.

Error Det

The output of the

feedback gate in

the PR Gen is ap-

plied to one input

of the Error Det,

which is another

exclusive-OR gate.

The second input to

the Error Det is the

data output from the

Data Fam Sel through

the Sel Data Retime.

After a number of

consecutive error-

free data bits

corresponding. to the

number of stages in

the shift register (3 in the example, 15 in the SG-1139), the

register will begin to output the same data pattern as the

input (the PR Gen is synchronized).

Whenever the input from the Data Fam Sel (data) differs from

that of the PR Gen (reference), the Error Det produces an output

(raw errors).